| 일 | 월 | 화 | 수 | 목 | 금 | 토 |

|---|---|---|---|---|---|---|

| 1 | 2 | 3 | 4 | 5 | 6 | 7 |

| 8 | 9 | 10 | 11 | 12 | 13 | 14 |

| 15 | 16 | 17 | 18 | 19 | 20 | 21 |

| 22 | 23 | 24 | 25 | 26 | 27 | 28 |

Tags

- Behavior Design Pattern

- 강한 연결 요소

- 최소 공통 조상

- map

- 그래프 탐색

- 게임 서버 아키텍처

- DP

- MongoDB

- 분리 집합

- Prisma

- Binary Lifting

- 자바스크립트

- LCA

- 벨만-포드

- Github

- 2-SAT

- Spin Lock

- localstorage

- PROJECT

- Strongly Connected Component

- Express.js

- ccw 알고리즘

- SCC

- trie

- JavaScript

- R 그래프

- 이분 탐색

- 비트필드를 이용한 dp

- 비트마스킹

- 트라이

Archives

- Today

- Total

dh_0e

[OS] Basic H/W Mechanisms (Bus, I/O Event, Handling and Device Access Mechanisms) 본문

Operating System

[OS] Basic H/W Mechanisms (Bus, I/O Event, Handling and Device Access Mechanisms)

dh_0e 2025. 11. 8. 23:47Computer Architecture(컴퓨터 구조)

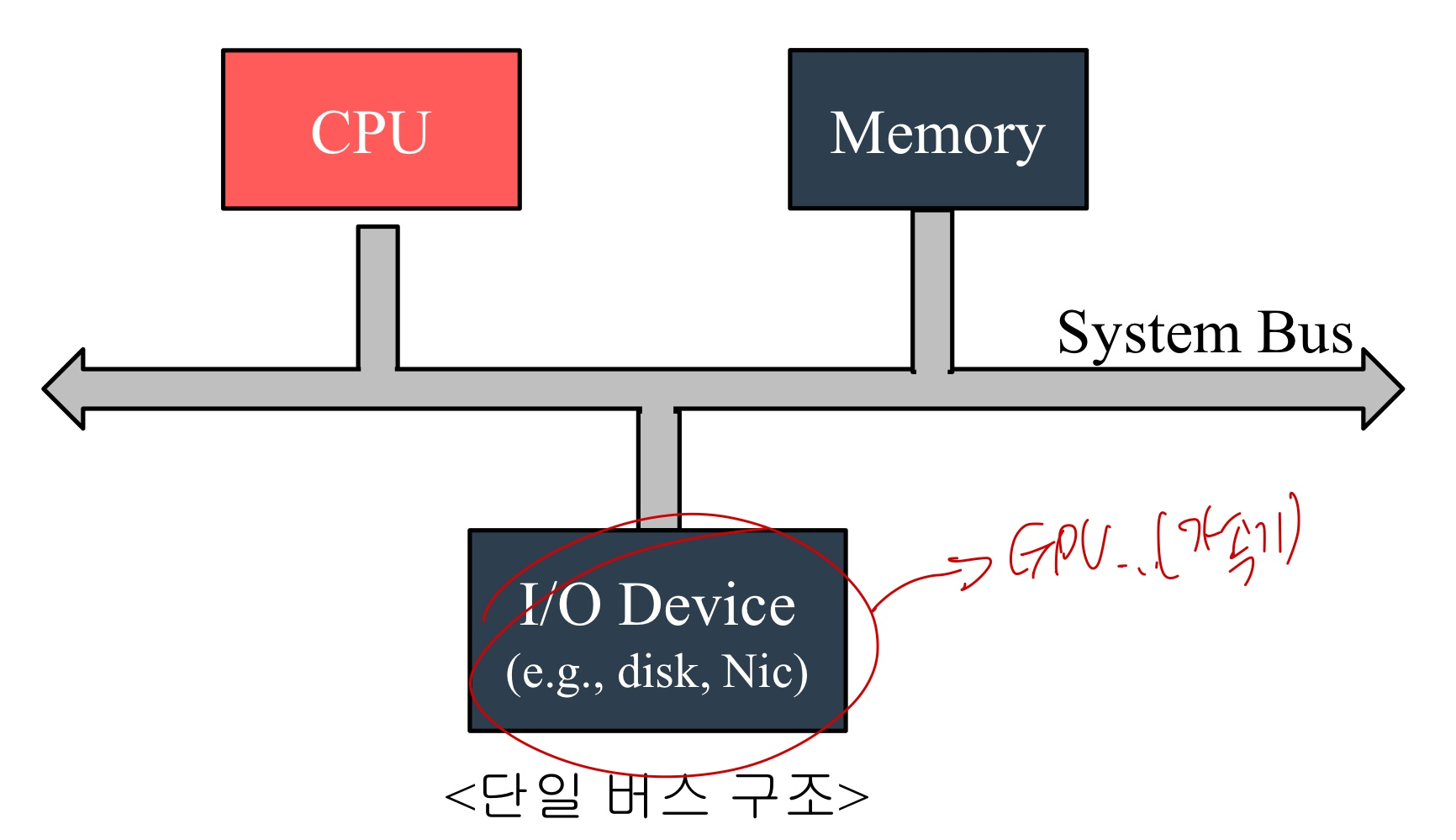

단일 Bus 구조

- Bus: CPU, RAM, I/O 장치 간 데이터가 전송되는 통로

- Data 버스, Address 버스

- 단일 Bus: 하나의 시스템 버스에 여러 가지 모듈이 연결

- CPU, Memory, I/O의 속도가 비슷했던 초창기에 발생

- 속도 격차가 증가(CPU > memory >>> I/O) → 병목 현상 발생

- 병목 현상: CPU가 쉬는 시간

- ex) CPU는 초당 5단위의 일 처리, 메모리 초당 3 단위의 일 처리를 할 수 있다면 전체 시스템 속도는 메모리의 속도(3)로 제한됨

- 병목 현상: CPU가 쉬는 시간

계층적 버스 구조

- 병목현상을 해결하기 위해 시스템 버스를 여러 개의 세분화된 버스로 나누는 방식 채용

- CPU Local Bus, Memory Bus, PCI Bus, etc.

- 이중 버스 구조: 현대 System 구조

- CPU와 I/O 속도 격차로 인한 병목 현상을 해결하고자 함

- 빠른 CPU와 메모리는 시스템 버스에 연결

- I/O 장치는 I/O 버스에 연결

Basic HW Mechanisms

- Event Handling Mechanisms: OS가 입출력 event를 처리하는 기법

- Interrupt: 비동기적 이벤트를 처리하기 위한 기법

- Trap: 동기적 예외를 처리하기위한 기법

- 즉, CPU가 "지금 뭔가 생겼다"라는 신호를 받는 메커니즘

- I/O Device Bassic Concept(입출력 장치 개념)

- CPU가 I/O 장치(디스크, 키보드, 네트워크 등)와 데이터를 주고받는 과정의 기본 아이디어

- CPU, I/O 장치 통신의 큰 그림, 골격

- I/O Handling Methods(입출력 처리 기법): 컴퓨터가 주변 장치(I/O 장치)와 데이터를 주고받을 때 사용하는 기본적인 방법

- Polling: CPU가 I/O 장치의 상태를 주기적으로 확인하여 작업 완료 여부를 검사하는 방식

- Dircet Memory Access(DMA): I/O 장치가 CPU의 개입 없이 직접 메모리에 접근하여 데이터를 전송하는 방식

- 즉, "I/O를 누가 관리하느냐"에 따른 차이

- 2번에서 데이터를 실제로 누가 어떻게 옮길 것인지

- I/O Device Access 기법(입출력 접근 방식)

- I/O Instruction: CPU가 별도의 입출력 명령어로 장치 접근

- Memory Mapped I/O: 입출력 장치를 메모리 주소 공간처럼 취급 (일반 load/store로 접근 가능)

- 즉, "I/O 장치에 데이터를 어떻게 주고받는가"의 차이

- 2번에서 CPU 명령어 관점에서 I/O 레지스터에 어떻게 접근할 것인지

1. 이벤트 처리 기법

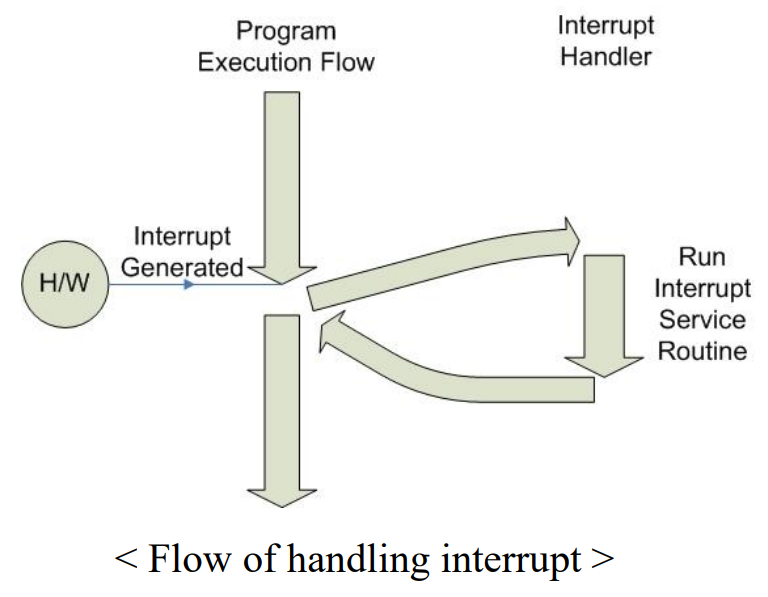

Interrupt (Handler)

- 비동기적(의도치 않은) 이벤트를 처리하기 위한 기법

- 비동기적 이벤트: 외부 장치(키보드, 마우스 등)의 요청이나 타이머 종료처럼 언제 일어날지 모르는 이벤트

- ex) 네트워크 패킷 도착 이벤트, I/O 요청

- 처리 순서

- Interrupt Disable: 일단 interrupt 막기

- 현재 실행 상태 저장: CPU가 interrupt가 발생하기 직전까지 수행하던 작업의 상태를 메모리에 저장

- ISR(Interrupt Service Routine)로 점프: 해당 interrupt를 처리하기 위해 ISR의 시작 주소로 점프하여 실행

- 저장한 실행 상태 복구: ISR이 완료되면, 2단계에서 저장했던 원래 작업의 상태 복원

- 인터럽트로 중단된 지점부터 다시 시작

- Interrupt에는 우선 순위가 있으며, H/W 장치마다 다르게 설정됨

- Note

- ISR은 짧아야 함: 너무 길면 다른 interrupt들이 제때 처리되지 못하고 지연될 수 있음

- 실행 중이던 Process 입장에서도 서운함

- Time Sharing은 Timer Interrupt의 도움으로 가능: 타이머 인터럽트를 통해 CPU를 공정하게 나누어 사용

- ISR은 짧아야 함: 너무 길면 다른 interrupt들이 제때 처리되지 못하고 지연될 수 있음

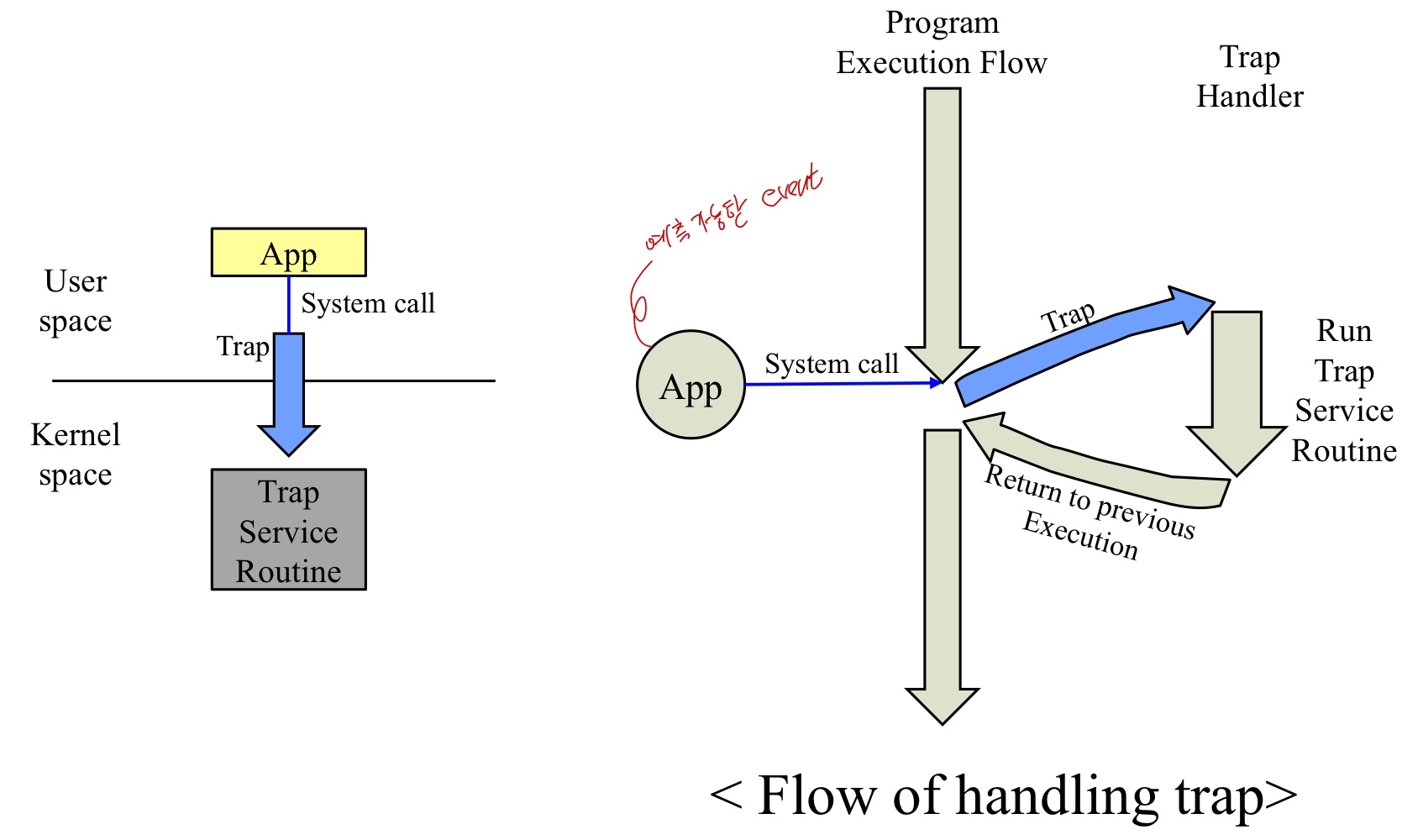

Trap

- 동기적 이벤트를 처리하는 기법

- 동기적 이벤트: Divide by Zero와 같은 프로그램 에러에 의해 발생하는 이벤트

- Trap handler에 의해 처리

- Trap Service Routine이 존재하여 Interrupt와 유사하지만, Interrupt와 달리 실행 상태를 저장/복원하지 않음

- 원래 상태로 돌아갈 필요 없이 그냥 다음으로 넘어가거나 에러 처리를 하면 됨

- User space의 App에서 System call이 발생하거나 Trap을 유발하는 명령 실행

- Trap이 발생하여 Kernel space로 진입

- Trap Handler가 Trap을 감지하고, Trap Service Routine을 실행하여 해당 이벤트를 처리

- 처리 완료 후, Return to previous Execution을 통해 이전 실행 흐름으로 복귀

Intel x86의 Interrupt & Exception

- Interrupt

- Hardware Interrupt

- 컴퓨터 밖의 장치(키보드, 마우스, 타이머 등)가 CPU에게 신호를 보내면 CPU가 하던 일을 잠시 멈추고 처리

- 칩셋에 의해 외부적으로 생성되며, CPU의 #INTR 핀에 신호를 전달하여 발생

- Software Interrupt

- 실행 중인 프로그램이 OS(커널)에게 특정 작업을 요청할 때 발생

- ex) 파일을 열거나 화면에 무언가를 출력하는 등의 System Call

- Hardware Interrupt

- Exception

- CPU가 어떤 명령을 실행하다가 오류를 발견했을 때 발생

- Fault(오류): 파일을 찾을 수 없거나(Page Fault), 0으로 나누는(Divide Err) 등의 문제로, 수정 후 다시 실행

- Trap: 디버깅 중 특정 지점에서 멈추거나(Breakpoint), 큰수로 인해 저장 공간이 넘치는(Overflow) 경우처럼, 의도적으로 멈춰서 추가 작업 수행

- Abort(중단): 하드웨어 고장(Machine Check)과 같이 복구 불가능한 심각한 오류가 발생하여 프로그램이나 시스템이 강제로 종료될 때 발생

XV6의 Interrupt & Exception

- XV6에서 하드웨어, 소프트웨어 Interrupt 모두 trap 메커니즘을 통해 처리됨

- Hardware Interrupt

- 인터럽트 벡터는 vector.S 파일에 저장됨

- IRQ_TIMER(타이머 인터럽트): 타이머로 프로세스 스케줄링을 결정

- IRQ_KBD(키보드 인터럽트): 키보드에서 어떤 글자가 입력되었는지 신호를 받고, 해당 글자를 처리

- IRQ_IDE(디스크 인터럽트): 파일 저장이나 불러오기 같은 디스크 작업이 끝나면 알려주는 인터럽트

- 입출력 장치에게 이 신호를 받으면 디스크 작업이 성공적으로 완료되었음을 확인하고, 다음 작업 진행

- Software Interrupt

- 사용자가 System call을 호출할 때, T_SYSCALL이라는 소프트웨어 인터럽트 발생

- ex) 워드 프로세서로 문서 저장을 누르면 OS에게 T_SYSCALL 발생시킴

2. I/O Device Basic Concepts (I/O 장치 기본 개념)

- Device Registers(장치 레지스터): 대부분의 H/W 장치는 4종류의 레지스터를 가짐

- Control Register: 장치의 동작을 제어, I/O에 값을 날려줌

- Status Register: 장치의 현재 상태를 나타냄

- Input Register: 장치로부터 입력된 데이터를 읽음

- Output Register: 장치로 데이터를 보내 출력

- Memory-mapped I/O: Register들은 메인 메모리 일부 영역에 매핑되어 CPU가 해당 주소를 통해 접근 가능

- I/O Controller

- Hige-Level의 I/O 요청을 Low-Level Machine Specific Instruction으로 해석하여 장치와 직접 상호작용하는 회로

- ex) 디스크의 특정 섹터에 데이터 쓰기 >> 디스크 컨트롤러가 장치 고유의 세부 명령으로 바꿔서 디스크에 전달

- CPU가 모든 종류의 장치를 직접 제어하는 방법을 알 필요 없게 해 줌

- 더 중요한 작업에 집중할 수 있음

- Hige-Level의 I/O 요청을 Low-Level Machine Specific Instruction으로 해석하여 장치와 직접 상호작용하는 회로

3. I/O Handling Methods(입출력 처리 기법)

Polling

- Loop 안에서 특정 이벤트의 도착 여부를 지속적으로 확인하며 기다리는 방법

- Loop 때문에 흔히 Programmed I/O(PIO)로 알려진 개념

- Interrupt Handler를 등록하는 방식과 반대되는 개념

- 매 순간 이벤트의 발생 여부 확인(Polling) vs 이벤트 요청받을 때만 한 번 확인(Interrupt Handler)

- Controller나 장치가 매우 빠른 경우에 event 처리 기법으로 적합함

- 단점

- 모든 연산이 CPU에 의해 진행: 이벤트 도착 시간이 길 경우, 귀중한 CPU Time을 낭비

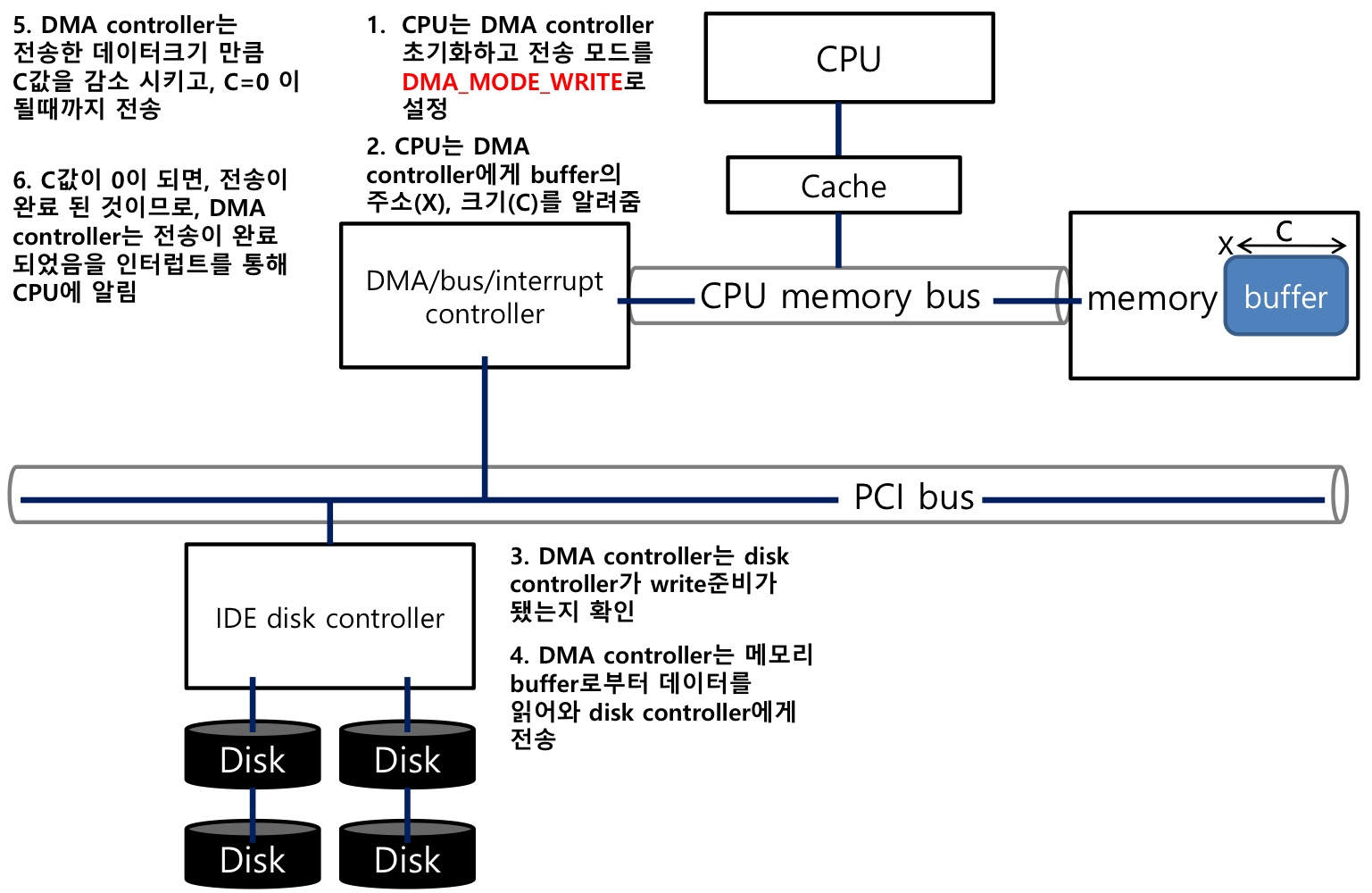

DMA(Direct Memory Access)

- 전송할 데이터가 클 경우, CPU가 Polling Time(PIO) 낭비

- DMA: 이 문제를 해결하기 위해 CPU를 대신하여 I/O를 수행하는 전용 프로세서

- 작동 방식

- CPU가 DMA Controller에게 I/O 요청

- DMA Controller는 CPU를 대신하여 I/O Device와 Main memory 사이의 데이터 전송을 직접 수행

- 장점

- CPU가 I/O 시간 동안 다른 일을 수행할 수 있음 >> CPU 효율성 증가

DMA vs Polling

| 특징 | DMA (Direct Memory Access) | Polling (폴링) |

| 개념 | "전문가에게 일을 맡기는 방식" (CPU가 지시 후 DMA 컨트롤러가 처리) | "CPU가 모든 것을 직접 확인하는 방식" (CPU가 계속 상태 확인) |

| 추가 하드웨어 | 필요 (DMA 컨트롤러) | 불필요 (CPU가 직접 확인) |

| 성능/효율성 | - CPU가 다른 중요한 일을 할 수 있음 - 동시 처리 (Parallelism)에 좋음 - 대량의 데이터를 빠르게 옮길 때 유용함 |

- CPU가 계속 주변 장치에 물어보며 기다림 - CPU 자원 소모가 많고 다른 일을 효율적으로 하기 어려움 - 비효율적일 수 있음 |

| 예시 | 스마트폰 카메라로 고해상도 사진을 찍을 때 (픽셀 데이터를 DMA 컨트롤러가 메모리로 직접 전송) | 아주 단순하고 느린 장치 (예: 키보드 Polling 처럼 버튼이 눌렸는지 확인하는 간단한 작업 ) |

| 장단점 요약 | - 장점: 큰 작업에 효율적, CPU 부담 적음 - 단점: 추가 하드웨어 필요 (비용 더 듦) |

- 장점: 작은 작업에 간단, 별도 하드웨어 불필요 (비용 덜 듦) - 단점: CPU 부담 큼, 대량 데이터 전송에 부적합 |

4. I/O Device Access 기법(입출력 접근 방식)

I/O Instruction

- Controller(I/O 장치의 제어 회로)는 데이터 및 신호 처리를 위해 1개 이상의 Register를 가짐

- Data, Control Signal을 처리하기 위함

- CPU는 Controller안에 Register의 Bit Pattern을 직접 읽고 씀으로써 장치와 통신함

- 이러한 기능을 수행하기 위해 I/O Instruction이 제공됨

- ex) Intel CPU의 I/O 명령어(in, out,..)

Memory Mapped I/O

- Device Register들을 Memory 공간에 Mapping 하여 사용

- Device Register가 메모리 주소에 매핑되면, 레지스터들이 주소 공간의 일부로 간주되어 사용됨

- 이때, 레지스터들이 (2)에서 나왔던 Device Regsisters들임

- CPU는 일반적인 명령어(mov, and, or,..)를 사용하여 I/O 작업을 수행

- ex) ARM CPU에는 별도의 I/O 명령어가 없고 주로 Memory Mapped I/O 방식을 사용

I/O Instruction vs Memory Mapped I/O

| 특징 | I/O Instruction | Memory Mapped I/O |

| 주소 공간 관리 | I/O 장치 레지스터를 위한 별도의 주소 공간 사용 | I/O 장치 레지스터를 메모리 주소 공간에 매핑 |

| CPU 접근 방식 | 특정 I/O 명령어를 사용하여 장치 레지스터에 접근 | 일반적인 메모리 접근 명령어를 사용하여 장치 레지스터에 접근 |

| 사용 명령어 예시 | Intel CPU의 in, out 명령어 | mov, and, or, xor 등 일반적인 데이터 처리 명령어 |

| 데이터 처리 | CPU가 컨트롤러의 레지스터 비트 패턴을 직접 읽고 씀 | 레지스터가 주소 공간의 일부로 취급되어 메모리처럼 다룸 |

Summary

- 컴퓨터 시스템의 전체적인 구성: 버스(bus)

- 버스(bus): 컴퓨터 내부의 다양한 하드웨어 구성 요소들(CPU, Memory, I/O 장치 등) 간에 데이터와 제어 신호를 주고받는 통로 역할

- I/O Events Mechanisms

- Interrupt: 외부에서 발생하는 비동기적 이벤트 (ex. 키보드, 마우스 같은 HW 장치가 CPU에게 인터럽트)

- Trap: 소프트웨어에서 발생하는 동기적 이벤트 (ex. 프로그램 실행 중 오류, System Call 등의 특정 상황)

- I/O Handling Mechanisms(입출력 처리 기법)

- Polling: CPU의 주기적으로 I/O 장치 상태를 직접 확인하는 방식

- DMA: CPU의 개입 없이 I/O 장치(DMA Controller)와 메모리가 직접 데이터를 주고받은 방식

- I/O Device Access 기법(입출력 접근 방식)

- I/O Instruction: CPU가 별도의 입출력 명령어로 장치 접근

- Memory Mapped I/O: 입출력 장치를 메모리 주소 공간처럼 취급하여 접근 (일반 명령어(load/store)로 접근 가능)

'Operating System' 카테고리의 다른 글

| [OS] IPC(Inter Process communication) (0) | 2025.11.14 |

|---|---|

| [OS] CPU Scheduling (1) | 2025.11.10 |

| [OS] Process, Context Switch (0) | 2025.11.06 |

| [OS] Operating System Structure, Kernel Designs (Monolithic, Micro, Hypervisor) (0) | 2025.11.03 |

| [OS] Operating System (0) | 2025.10.01 |